Journal of Artificial Intelligence and Data Mining (JAIDM) Journal homepage: http://jad.shahroodut.ac.ir

**Research** paper

# Low-order Robust Controller for DC-DC Quadratic Buck Converter: Design and Implementation

Ali Sedehi<sup>1</sup>, Alireza Alfi<sup>1\*</sup> and Mohammadreza Mirjafari<sup>2</sup>

1. Faculty of Electrical Engineering, Shahrood University of Technology, Shahrood, Iran. School of Science, Engineering, and Technology, Penn State University, Pennsylvania, United States.

#### Article Info

### Abstract

# Article History:

Received 10 September 2023 Revised 12 January 2024 Accepted 24 January 2024

DOI:10.22044/jadm.2024.13584.247

#### Keywords:

Quadratic Buck Converter, µ Synthesis, Order Reduction, Robust Controller, Optimization.

\*Corresponding author: a\_alif@yahoo.com (A. Alfi). This paper addresses a key challenge in designing a suitable controller for DC-DC converters to regulate the output voltage effectively within a limited time frame. In addition to non-minimum phase behavior of such type of converter, a significant issue, namely parametric uncertainty, can further complicate this task. Robust control theory is an efficient approach to deal with this problem. However, its implementation often requires high-order controllers, which may not be practical due to hardware and computational constraints. Here, we propose a low-order robust controller satisfying the robust stability and performance criteria of conventional highorder controllers. To tackle this issue, a constraint optimization problem is formulated, and the evolutionary algorithms are adopted to achieve the optimal parameter values of the controller. Both simulation and experimental outcomes have been documented, and a comparative analysis with an optimal Proportional-Integral (PI) controller has been conducted to substantiate efficiency to the proposed methodology.

### 1. Introduction

Recently, the extensive utilization of DC-DC converters in various applications such as DC microgrids, storage batteries, wind turbines, photovoltaic systems, and LED lamp drivers has promoted to the exploration of different converter topologies including step-down and step-up configurations [1-7]. These converters exhibit nonlinear behavior with a time-varying structure due to their switching operation, making it challenging to satisfactory performance achieve using conventional linear methods over a wide range of operation [8]. Consequently, the design of controllers for these converters has garnered significant interest, with researchers employing diverse control techniques to regulate voltage. Several studies have been documented in the literature, encompassing approaches such as the Kharitonov theorem [9, 10], fuzzy logic control [11-15], fractional control [16, 17], linearquadratic regulator (LQR) [18, 19], adaptive backstepping control [20-22], sliding mode control

techniques [23-26], and feedback linearization control [27].

The objectives of system performance and voltage regulation objectives are affected by parameter perturbations stemming from uncertainties. Consequently, it becomes imperative to address these uncertainties to meet performance and stability criteria [28]. Robust control theory has emerged as a widely recognized methodology to achieve these objectives.  $\mu$ -synthesis is a key technique for designing a robust controller that utilizes the structured singular value (SSV). Through this method, two goals involving robust stability (RS) and robust performance (RP) can be guaranteed against different types of uncertainties [29]. A linearized model of the system is required to design a controller using this approach. For representing the performance specifications of the closed-loop system and shaping the exogenous signals, multiple weighting functions may be included. This has been method confirmed to

provide much better performance than conventional controllers [30]. The DK iteration algorithm has emerged as the predominant approach for addressing the  $\mu$ -synthesis problem in conventional methods. However, this approach yields a controller with a high-order, which could pose challenges for real-time implementation due to constraints imposed by hardware and computational capabilities.

Additionally, it should be noted that in certain scenarios, this algorithm has the potential to converge towards local minima [31]. A systematic procedure to avoid high-order controllers is to reduce the order of controller through model order reduction. However, this reduction can often degrade criteria robustness and system performance [32]. One potential approach to address the previously mentioned problems involves the utilization of a fixed-structure robust controller. This method offers a practical and lower-order controller to effectively implement the system [33, 34]. To acquire the parameters for the low-order controller, a constraint optimization problem is proposed, and heuristic algorithms employed to solve it. These algorithms have garnered significant attention in their advancement [34, 36]. [37] Used Particle Swarm Optimization (PSO) to obtain parameters of low-order controller designed based on the Kharitonov approach for a buck converter with an order of two and no zero or pole situated on the right-half plane. Besides advantages of this method, it should be mentioned that the complexity to determine acceptable bounds for the parameters of the controller significantly increases if the order of the system or controller grows.

step-down DC-DC converters, Among the Ouadratic Buck Converter (OBC) has the ability to reduce the level of input voltage considerably. The main contribution of this article is to design a loworder robust controller for a DC-DC QBC converter, which suffers from uncertainties in its parameters. The validity of the designed controller is verified by conducting a comparative analysis with two widely used methods: the DK iteration method, which is a conventional approach for addressing the  $\mu$ -synthesis problem, and an optimal PI controller. Simulations illustrate the appropriate behaviour of the proposed control algorithm for voltage regulation. The difference in order between the proposed controller and the resultant controller by DK iteration provides a simplicity to implementation on a Micro Controller Unit (MCU).

The remainder of this article is structured as what follows. In Section 2, an extracted small signal

averaged model of the converter is presented, followed by the discussion of approaches for designing a robust controller. Sections 3 and 4 detail simulations and the experiments, respectively. The last section provides conclusions regarding key aspects and remarks.

## 2. Problem Formulation

In this section, the design of a robust controller based on  $\mu$  synthesis is discussed. The conventional method for solving an optimization problem to obtain a robust controller leads to a high-order controller. This makes it difficult to implement in practice. The proposed robust fixedstructure controller based on  $\mu$  can be a suitable solution to avoid high-order counterpart, which maintains the feature of the resultant controller by DK iteration beside its considerable low order. In this section, first, the system description of the DC-DC quadratic buck converter is presented, and preliminaries of the designed controller are described in section B. Then the proposed method to the low-order controller is studied.

## 2.1. System description

The quadratic buck converter is equivalent to two conventional buck converters arranged in cascade, featuring only a single active and three passive switches. This converter comprises two inductors and two capacitors, making it a fourth-order system. The conversion ratio in Continuous Conduction Mode (CCM) is determined by the following equation:

$$\frac{V_o}{V_{in}} = D^2 \tag{1}$$

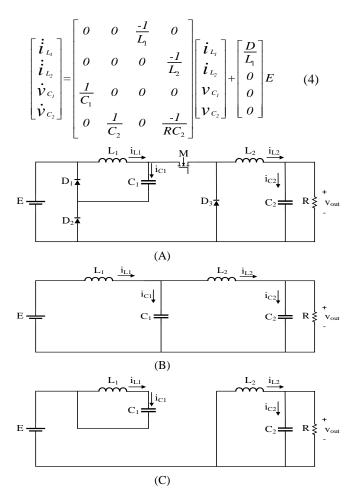

In comparison with a conventional buck converter, a quadratic buck offers a wider conversion ratio and can achieve lower voltage at the same duty cycle. Prior to designing a controller, it is essential to establish a dynamic model for the converter. The average model techniques, as outlined in [38], have been employed to derive the dynamic equations of the converter. This approach is widely used for modeling power electronic circuits in both continuous and discontinuous conduction modes [39]. As shown in the topology of the circuit in Figure 1(a), there are two low-pass filters:  $L_1$  and  $C_1$  in the first stage,  $L_2$  and  $C_2$  in the second stage. The variables of the QBC are the voltage of capacitors and the current of inductors. In CCM, QBC works in two operation modes, as depicted in Figures 1(a) and 1(b). The first mode is active when the switch is on. In this stage, diodes  $D_1$  and  $D_3$  are open, and  $D_2$  is conducting. The capacitors  $C_1$  and C<sub>2</sub> are charged and discharged, respectively, and the inductor L1 is charged by source E. The statespace equation of this operation mode is described by Eq. (2). In the second mode, when the switch is off, diodes  $D_1$  and  $D_3$  are on, and  $D_2$  is off.

$$\begin{bmatrix} \mathbf{i}_{L_{l}} \\ \mathbf{i}_{L_{2}} \\ \mathbf{v}_{C_{1}} \\ \mathbf{v}_{C_{2}} \end{bmatrix} = \begin{bmatrix} 0 & 0 & \frac{-1}{L_{1}} & 0 \\ 0 & 0 & \frac{1}{L_{2}} & \frac{-1}{L_{2}} \\ \frac{1}{C_{2}} & \frac{-1}{C_{1}} & 0 & 0 \\ 0 & \frac{1}{C_{2}} & 0 & \frac{-1}{RC_{2}} \end{bmatrix} \begin{bmatrix} \mathbf{i}_{L_{1}} \\ \mathbf{i}_{L_{2}} \\ \mathbf{v}_{C_{1}} \\ \mathbf{v}_{C_{2}} \end{bmatrix} + \begin{bmatrix} \frac{1}{L_{1}} \\ 0 \\ 0 \\ 0 \end{bmatrix} E \qquad (2)$$

In this stage, capacitors are charged by inductors. The state-space equation related to this mode is given by:

$$\begin{bmatrix} \dot{i}_{L_{l}} \\ \dot{i}_{L_{2}} \\ \dot{v}_{C_{l}} \end{bmatrix} = \begin{bmatrix} 0 & 0 & \frac{-1}{L_{1}} & 0 \\ 0 & 0 & 0 & \frac{-1}{L_{2}} \\ \frac{1}{C_{l}} & 0 & 0 & 0 \\ 0 & \frac{1}{C_{2}} & 0 & \frac{-1}{RC_{2}} \end{bmatrix} \begin{bmatrix} \dot{i}_{L_{l}} \\ \dot{i}_{L_{2}} \\ v_{C_{l}} \\ v_{C_{l}} \end{bmatrix} + \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix} E \qquad (3)$$

By integrating Eqs. (2) and (3), the average nonlinear equation of the QBC is extracted as:

Figure 1. (A) Quadratic buck converter circuit topology, (B) The switch is on, (C) The switch is off.

The equilibrium point of the converter in the nominal situation is given by:

$$V_{C1e} = ED, \ V_{C2e} = ED^2, \ I_{L1e} = \frac{ED^3}{R}, \ I_{L2e} = \frac{ED^2}{R}$$

(5)

Considering the small perturbations in all steadystate variables and the duty cycle of the QBC, the small signal model is derived as:

$$\begin{bmatrix} \dot{\vec{i}}_{L_{l}} \\ \dot{\vec{i}}_{L_{2}} \\ \dot{\vec{v}}_{C_{l}} \\ \dot{\vec{v}}_{C_{2}} \end{bmatrix} = \begin{bmatrix} 0 & 0 & \frac{-1}{L_{1}} & 0 \\ 0 & 0 & \frac{D}{L_{1}} & \frac{-1}{L_{2}} \\ \frac{1}{C_{1}} & \frac{-D}{C_{1}} & 0 & 0 \\ 0 & \frac{1}{C_{2}} & 0 & \frac{-1}{RC_{2}} \end{bmatrix} \begin{bmatrix} \tilde{i}_{L_{l}} \\ \tilde{i}_{L_{2}} \\ \tilde{v}_{C_{l}} \\ \tilde{v}_{C_{2}} \end{bmatrix} + \begin{bmatrix} \frac{E}{L_{l}} \\ \frac{V_{Cle}}{L_{2}} \\ \frac{-\frac{L_{2e}}{C_{1}}}{0} \end{bmatrix} \tilde{d}$$

(6)

Where *E* denotes the input voltage,  $\tilde{d}$  corresponds to the control signal of the converter, which takes a valid range of [0, 1], and *R* represents the load resistance. The output voltage corresponds to the capacitor voltage in the second stage is  $V_{c2e} = V_o$ . The small signal transfer function from control signal (duty cycle) to output voltage is derived by applying Laplace transform, which is represented as [40]:

$$T_{QBC} = \frac{\tilde{v}_O}{\tilde{d}} = \frac{V_{C2e}}{DC_2L_2} \times \frac{s^2 + a_1 s + a_0}{s^4 + b_1 s^3 + b_2 s^2 + b_3 s + b_4}$$

(7)

Where:

$$b_{0} = \frac{1}{L_{1}C_{1}L_{2}C_{2}}, \quad b_{1} = \frac{1}{RC_{2}}, \quad b_{2} = \frac{D^{2}}{C_{1}L_{2}} + \frac{1}{L_{2}C_{2}} + \frac{1}{L_{1}C_{1}}$$

$$b_{3} = \frac{D^{2}}{RC_{1}L_{2}C_{2}} + \frac{1}{RL_{1}C_{1}C_{2}}, \quad a_{1} = -\frac{D^{2}}{RC_{1}}, \quad a_{0} = \frac{2}{L_{1}C_{1}}$$

(8)

It is apparent that the transfer function (7) has two zeros, which are located in the right-half plane (RHP). This imposes a critical limitation on bandwidth, and satisfactory performance will be difficult to achieve. The nominal values and the range of uncertainty on the circuit's parameters are listed in Table 1.

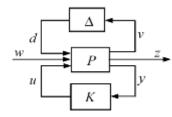

#### 2.2 Preliminaries

A common representation of a closed-loop system experiencing uncertainties and external inputs can be visualized through an interconnected system, as demonstrated in Figure 2. Within the present conceptual framework, exogenous inputs including reference signals, noise, and disturbances are represented as "w", while the output error, which involves the control actions, tracking errors, and the regular output, is denoted by "z". The known component of the system, comprising the nominal plant and weighting functions, is represented by "P", with "K" referring to the controller. The uncertainty set is visually depicted by " $\Delta$ ". Additionally, the input and output signals associated with the dynamic uncertainties are designated as "v" and "d", respectively. The general framework in Figure 2 can be simplified by a lower linear fractional transformation of P and K,  $M(P, K) = F_1(P, K)$ , as is shown in Figure 3.

| Parameter      | Nominal value | Range of uncertainty |

|----------------|---------------|----------------------|

| R              | 5Ω            | [-20% , 20%]         |

| $L_1$          | 470μ          | [-30% , 30%]         |

| L <sub>2</sub> | 330µ          | [-30% , 30%]         |

| C <sub>1</sub> | 33μ           | [-30% , 30%]         |

| C <sub>2</sub> | 100μ          | [-30%, 30%]          |

| Е              | 12v           | [8 ~ 16]             |

| $f_{sw}$       | 62.5kHz       | -                    |

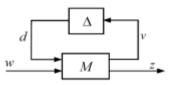

In this structure, the closed-loop system is influenced by exogenous inputs and uncertainties. According to the concept of structured singular value ( $\mu$ ), the closed-loop stability of a system can be determined. The system is considered robustly stable if and only if it is internally stable, and the maximum upper structured singular value of the first component of the matrix *M* is less than unity [41].

$$\mu_{\Lambda}(M_{11}) < 1$$

(9)

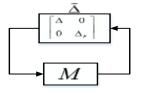

The tool employs a robust performance analysis approach by incorporating a fictitious uncertainty block, denoted by  $\Delta_F$ , which encompasses the system's performance specifications. Blocks  $\Delta_F$ and  $\Delta$  are merged and converted to  $\tilde{\Delta}$ , as seen in Figure 4. Based on the given configuration, the closed-loop system is considered to have robust performance if the condition described by Equation (10) is satisfied.

$$\mu_{\tilde{\Delta}}(M) < 1 \tag{10}$$

The common technique for solving the  $\mu$  synthesis problem is the *DK* iteration approach. This converter comprises two inductors and two capacitors, making it a fourth-order system. In each stage, an  $H_{\infty}$  optimization problem is solved for a fixed given matrix *D* to get controller *K*. Subsequently, the controller is set and a convex optimization problem is solved within a specified frequency range to determine *D*. This iterative process continues until the maximum structured singular value of the closed-loop system is reduced below unity. However, there are two main limitations associated with this method. Firstly, there is a risk of the algorithm converging to local minima. Secondly, it may result in the generation of a high-order controller that is noticeable in the system.

Figure 2. General framework [38].

Figure 3. Robust stability analysis [38].

Figure 4. Robust performance analysis [38].

### 2.3 Proposed method

In order to address the challenges associated with the high-order controller resulting from the DKiteration method, this section proposes a solution in the form of a constraint optimization method. By this approach, one can select the arbitrary loworder control structure, while the resultant controller satisfies the robust conditions described by (9) and (10), even though, it can carry the characteristics of the high-order controller. The proposed method to avoid the high-order controller is a constraint optimization problem such that the resultant controller satisfies both robust stability and robust performance conditions, while its order is dramatically lower than the controller by the DK method. Generally, a known simple structure is selected for the controller as low-order as possible, and the controller's parameters are determined through evolutionary algorithms for solving the pre-defined optimization problem. In this manuscript. present the subsequent we optimization problem.

$$\begin{split} \min_{K(s)} & \left\| M(s) \right\|_{\mu} \\ \text{such that:} & \left\| M_{11}(s) \right\|_{\mu} < 1 \end{split} \tag{11}$$

In this context, the robust stability (9) is formulated as a constraint optimization, while the robust performance condition (10) is regarded as the fitness function.

#### **3. Simulation Results**

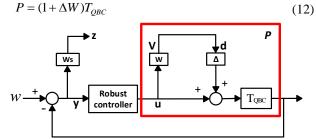

Besides the non-minimum phase behavior of the converter, another challenging issue is the existence of uncertainty in the parameters of the circuit, which poses difficulties in regulating the output voltage. To account for model uncertainty, the multiplicative uncertainty description given by equation (12) is employed. Figure 5 illustrates the closed-loop system with uncertainty.

Figure 5. Block diagram of closed-loop uncertain system.

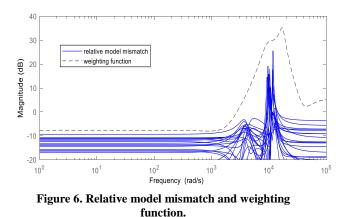

In Figure 5, W,  $W_s$ , and  $\Delta$  represent the weighting function, the performance function, and the perturbation. respectively. unknown It is considered that  $\Delta$  is a norm-bounded, where its infinity norm is smaller than or equal to unity. Through multiplicative uncertainty description and the determination of its maximum value, it can be proven that W is greater than any relative model mismatch across all frequency ranges. Figure 6 demonstrates the behavior of multiplicative uncertainty and the corresponding weighting function. Equations (13) and (14) describe the weighting and the performance functions, respectively.

Equation (15) describes the controller through the DK iteration. As can be seen, the resulting controller has an order 17, posing challenges for

both analog implementation using op-amps or digital implementation on microcontrollers.

$$W_{s} = \frac{0.1 \text{ s} + 478}{1.283 \text{ s} + 4.78 \times 10^{-5}}$$

(13)

$$W = \frac{2.028s^4 + 4.742 \times 10^4 s^3 + 3.18 \times 10^9 s^2 + 6.901 \times 10^{12} s + 1.032 \times 10^{16}}{s^4 + 8105s^3 + 3.963 \times 10^8 s^2 + 1.667 \times 10^{12} s + 2.514 \times 10^{16}}$$

(14)

$$K_{DK} = \frac{N_1 N_2}{D_1 D_2}$$

(15)

Where:

$$\begin{split} N_1 &= 2134.8(s^2 + 2832s + 4.347 \times 10^6)(s^2 + 5179s + 1.041 \times 10^7) \\ &(s^2 + 1796s + 1.312 \times 10^7)(s^2 + 1849s + 1.921 \times 10^7) \\ N_2 &= (s^2 + 4653s + 8.521 \times 10^7)(s^2 - 3559s + 1.573 \times 10^8) \\ &(s^2 + 3452s + 2.95 \times 10^8)(s^2 + 2.475 \times 10^4 s + 5.599 \times 10^8) \\ D_1 &= (s + 3.726 \times 10^{-5})(s^2 + 2705s + 4.22 \times 10^6)(s^2 + 5241s + 9.978 \times 10^6) \\ &(s^2 + 3680s + 7.392 \times 10^6)(s^2 + 1808s + 1.361 \times 10^7) \\ D_2 &= (s^2 + 2521s + 1.498 \times 10^8)(s^2 + 2.247 \times 10^4 s + 6.205 \times 10^8) \\ &(s^2 + 5.965 \times 10^4 s + 2.131 \times 10^9)(s^2 + 2.111 \times 10^4 s + 1.508 \times 10^9) \end{split}$$

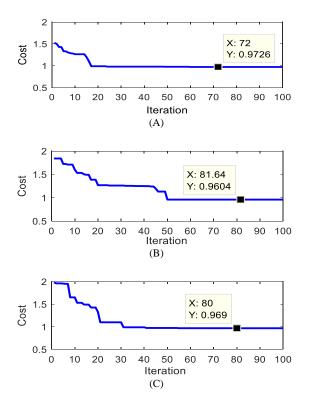

To avoid the high-order controller, we apply he proposed method, which formulates a constraint optimization problem to ensure that the resulting controller satisfies both robust stability and robust performance conditions. Additionally, the order of controller is significantly lower compared to the controller obtained through the *DK* method. In this method, a specified structure is chosen for the controller, and evolutionary algorithms are adopted to determine the parameters of the controller. The optimization constraint is based on robust stability using  $\mu$ , with robust performance considered as the cost function. In this study, for a more comprehensive comparison, three well-known optimization algorithms, namely ant bee colony (ABC), genetic algorithm (GA), and particle swarm optimization (PSO) [42], are utilized. The proposed structure for the low-order controller is described in Equation (16) with four parameters. The range of values for each parameter is listed in Table 2.

$$K_{proposed} = \frac{as+b}{s^2+cs+d} \tag{16}$$

Table 2. Search space of the parameters of controller.

| Parameter | а             | b         | с         | d            |

|-----------|---------------|-----------|-----------|--------------|

| Range     | $[0\sim 100]$ | [0 ~ 1e5] | [0 ~ 1e3] | $[0 \sim 1]$ |

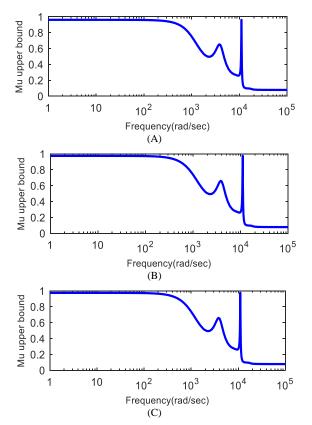

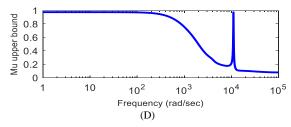

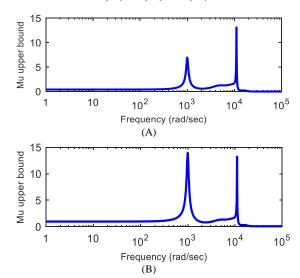

The number of iteration of all algorithms is set to 100. Figure 7 shows the convergence rate of the cost function for PSO, GA, and ABC, respectively. For better evaluation, the controller that has been synthesized by DK iteration is reduced by the Hankel norm to the same order with the proposed structure. All low-order controller parameters are listed in Table 3. Robust stability and performance of the robust controllers based on  $\mu$  analysis are

represented in Figures 8 and 9, respectively. As can be seen, the proposed controller, designed using three algorithms, satisfies both robust conditions. However, the reduced-order controller, determined by the Hankel norm and having the same order as the proposed controller, does not meet the criteria for robust stability and performance, as illustrated in Figure 10.

Figure 7. Convergence of cost function by algorithms. A) ABC, B) GA, C) PSO.

Table 3. Parameters of the low-order proposed controller.

| Method - | Parameters |          |         |         |

|----------|------------|----------|---------|---------|

|          | а          | b        | с       | d       |

| PSO      | 0.06102    | 9.312e4  | 2157    | 0.05483 |

| GA       | 0.05603    | 9.213e4  | 2106.5  | 0.01734 |

| ABC      | 0.05534    | 9.3916e4 | 2201.67 | 0.05407 |

| Hankel   | -88.59     | 7.179e4  | 1692    | 0.06301 |

The maximum structured singular values for the robust stability and performance, for all controllers under discussion are summarized in Table 4. It is readily that a better stability and performance margin is reached by the proposed method in comparison with DK iteration, so the proposed controller could inherit the behavior of a robust high-order controller besides has a more simple structure. To validate the controllers, each controller is put on a non-linear physical model of a circuit in the Simulink environment. To more comparison between the proposed controller and the high-order controller, the PI controller is

designed whose parameters are extracted by PSO algorithms.

Table 4. Maximum SSV for RS and RP of controllers.

| Method | RS      | RP      |

|--------|---------|---------|

| PSO    | 0.8832  | 0.9690  |

| ABC    | 0.8819  | 0.9726  |

| GA     | 0.8746  | 0.9604  |

| DK     | 0.8945  | 0.9770  |

| Hankel | 13.1062 | 13.9470 |

The cost function for this optimization problem is based on integral absolute error (IAE). The structure of PI controller is as:

$$C = K_p \left(1 + \frac{1}{K_i s}\right) \tag{17}$$

Where:

$K_n = 0.0343$   $K_i = 9.385929 \times 10^{-4}$  (18)

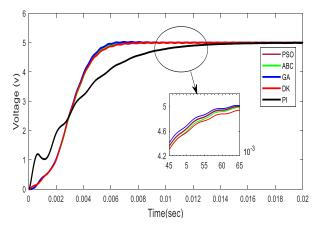

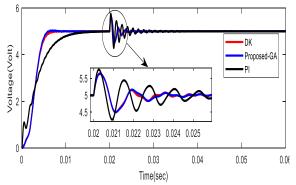

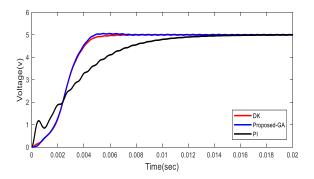

In simulation, different scenarios are executed. Initially, all circuit parameters are set to their nominal values. Subsequently, the impact of set point changes is examined. Following that, the system's performance is investigated under variations in the resistance load. The circuit is then subjected to the worst-case scenario, considering uncertainties. Figure 11 illustrates the output voltage regulation at the desired 5V for all controllers. As observed, there is a nearly identical transient response for all the proposed low-order controllers. However, the parameters that have been obtained by GA provides a quicker response compared to others by PSO and ABC algorithms. Moreover, the proposed controllers not only meet the robustness criterion and maintain the performance of high-order robust controllers but also have a better response. This observation is significant, particularly indicating that the approach for deriving low-order controllers is more practical. Additionally, it facilitates the implementation of controller coding in the C language for microcontroller.

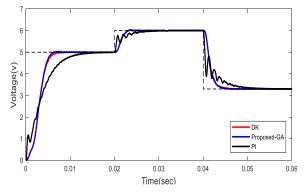

In the following, the parameters extracted by GA are considered as the proposed controllers and compare with the conventional DK iteration and PI. The ability to track the set point changing of controllers is shown in Figure 12. The desired output voltage is changed to 6V at t = 0.02 s, and then it is switched to 3.3V at t = 0.04. It is obvious that the robust controllers can track various voltage levels properly without oscillation and faster than PI. In the next step, the effect of uncertainty on the resistance load is analyzed. In this scenario, the resistive load is changed from 4 to 6 at t = 0.02 s, and the output response is illustrated in Figure 13. It can be seen that the robust controllers return faster the output voltage to the initial state after a step change in the load and the output experiences smaller overshoot in comparison with PI.

Figure 8. Robust stability analysis based on μ. A) ABC, B) GA, C) PSO, D) DK.

Figure 9. Robust performance analysis based on  $\mu$ . A) ABC, B) GA, C) PSO, D) *DK*.

Figure 10. Robust stability and performance analysis based on from reduced-order by Hankel. A) robust stability, B) robust performance.

In terms of uncertainty, the converter is considered with the worst-case when parameters of the converter are deviated from their nominal values as follows:

$$R = 6\Omega \qquad L_1 = 329\,\mu H \qquad L_2 = 429\,\mu H C_1 = 23.1\mu F \qquad C_2 = 130\,\mu F \qquad E = 16v$$

(19)

Figure 11. Output voltage for nominal situation.

Figure 14 depicts the output voltage under the worst-case situation, and the proposed controller behavior shows an acceptable response to output voltage regulation. Totally, it concludes that the proposed controller can realize proper characteristics of the resultant high-order controller

by powerful *DK* iteration tool while the difference order between them is considerable.

#### 4. Experimental Results

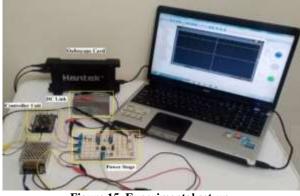

In this section, the effectiveness of the proposed robust controller is investigated. The first step involves discretization of the controller, which has been carried out using Tustin's method with sample time 100 us. For the unit controller, a STM32F103RET6 is used.

Figure 12. Reference tracking.

Figure 13. Resistance load changing.

Figure 14. Output voltage for worst case situation.

To generate the PWM control signal for hardware QBC, a sawtooth signal with 62.5 kHz frequency is compared with the extracted signal from the controller's equation, and, therefore, an appropriated square signal is generated. The hardware schematic of the quadratic buck converter is shown in Figure 15 including the power stage, the control unit, the DC power supply,

and the oscilloscope card. The power unit involves a Mosfet IRF540 and IR2104 as switch and gate driver, respectively.

Figure 15. Experimental set-up.

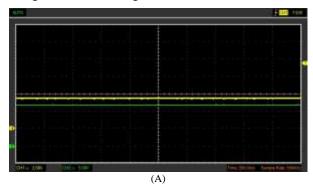

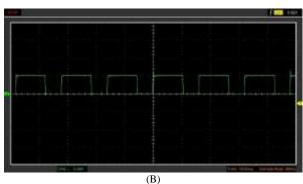

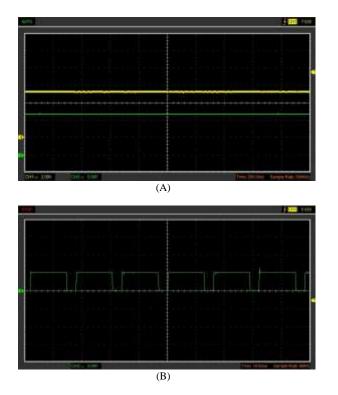

The output voltage of the converter and control signal for different voltage levels are illustrated in Figures 16 and 17. In Figure 16(a) and 17(A), the input voltage source (CH2) is 12V, and the output voltage (CH1) for voltage levels are 3.3 V and 5 V, respectively. The related PWM signal produced by the controller to trigger the Mosfet for desired voltage is shown in Figures 16(b) and 17(b).

Figure 16. Set point 3.3V. (A) Output voltage, (B) Control signal.

### 5. Conclusion

In this paper, a robust low-order controller with a simple structure for a quadratic buck converter is proposed. Evolutionary algorithms have been employed to determine the parameters of the proposed controller by solving a predefined constraint optimization problem. The genetic algorithm exhibits superior performance in terms of stability and performance margin based on  $\mu$ . Unlike the model order reduction Hankel method, this controller has carried properly the characteristics of the robust high-order controller by conventional DK approach without any degradation of the system performance. In comparison with PSO-based PI controller, the proposed controller has better convergence to reference voltage, and smaller recovery time in the situation of parameters changing. Thanks to the proposed controller's low-order structure, it is more convenient to implement on the Microcontroller unit controller. Simulation and experimental results confirmed the ability of the proposed robust loworder controller to maintain output voltage on desired levels.

Figure 17. Set point 5 V. (A) Output voltage, (B) Control signal.

### References

[1] M. Mirjafari, M. Banejad, and H. Molla-Ahmadian, A. Sedehi, and F. Blaabjerg, "Robust stability analysis of a novel droop-based distributed control scheme for islanded operation of DC microgrids," *IET Renewable Power Generation*, vol. 16, no. 15, pp. 3325-3338, 2022.

[2] T. K. Nizami, and C. Mahanta, "An intelligent adaptive control of DC–DC buck converters," *Journal of the Franklin Institute*, vol. 353, no. 12, pp. 2588-2613, 2016.

[3] Y.-C. Hsu, C.-Y. Ting, L.-S. Hsu, J.-Y. Lin, and C. C.-P. Chen, "A Transient Enhancement DC–DC Buck Converter With Dual Operating Modes Control

Technique," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 66, no. 8, pp. 1376-1380, 2018.

[4] N. Zerroug, M. N. Harmas, S. Benaggoune, Z. Bouchama, and K. Zehar, "DSP-based implementation of fast terminal synergetic control for a DC–DC Buck converter," *Journal of the Franklin Institute*, vol. 355, no. 5, pp. 2329-2343, 2018.

[5] A. Dali, S. Diaf, and M. Tadjine, "Maximum Power Tracking and Current Control for Solar Photovoltaic System Applications, Hybrid Dynamical System Approach," *Journal of Dynamic Systems, Measurement, and Control*, vol. 141, no. 9, 2019.

[6] I. Sudiharto, M. I. Rahadyan, and O. A. Qudsi, "Design and Implementation of Buck Converter for Fast Charging with Fuzzy Logic," *JAREE (Journal on Advanced Research in Electrical Engineering)*, vol. 5, no. 1, 2021.

[7] A. Dastgiri, M. Hosseinpour, F. Sedaghati, and S. R. Mousavi-Aghdam, "A high step-up DC–DC converter with active switched LC-network and voltage-lift circuit: topology, operating principle, and implementation," *International Journal of Circuit Theory and Applications*, vol. 50, no. 1, pp. 226-248, 2022.

[8] H. Al-Baidhani, M. K. Kazimierczuk, and A. Reatti, "Nonlinear modeling and voltage-mode control of DC-DC boost converter for CCM," *In IEEE Int. Symposium on Circuits and Systems (ISCAS)*, Italy, 2018, pp. 1-5.

[9] F. Asadi, and N. Abut, "Kharitonov's theorem: A good starting point for robust control," *The International Journal of Electrical Engineering & Education*, pp. 0020720919829708, 2019.

[10] H. Bevrani, P. Babahajyani, F. Habibi, and T. Hiyama, "Robust control design and implementation for a quadratic buck converter," *The 2010 International Power Electronics Conference-ECCE ASIA*, 2010, pp. 99-103.

[11] M. Rakhshan, N. Vafamand, M.-H. Khooban, and F. Blaabjerg, "Maximum power point tracking control of photovoltaic systems: A polynomial fuzzy modelbased approach," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 6, no. 1, pp. 292-299, 2017.

[12] J. P. Ram, T. S. Babu, and N. Rajasekar, "A comprehensive review on solar PV maximum power point tracking techniques," *Renewable and Sustainable Energy Reviews*, vol. 67, pp. 826-847, 2017.

[13] D. Guiza, Y. Soufi, D. Ounnas, and A. Metatla, "Design and Implementation of Takagi-Sugeno Fuzzy Tracking Control for a DC-DC Buck Converter," no. 3, pp. 234-243, 2019.

[14] A. Benzaouia, F. Mesquine, M. Benhayoun, H. Schulte, and S. Georg, "Stabilization of positive constrained T–S fuzzy systems: Application to a Buck converter," *Journal of the Franklin Institute*, vol. 351, no. 8, pp. 4111-4123, 2014.

[15] C. H. Basha, and M. Murali, "A new design of transformerless, non-isolated, high step-up DC-DC converter with hybrid fuzzy logic MPPT controller," *International Journal of Circuit Theory and Applications*, vol. 50, no. 1, pp. 272-297, 2022.

[16] A. M. Movahed, H. T. Shandiz, and S. K. Hosseini Sani, "Comparison of fractional order modelling and integer order modelling of fractional order buck converter in continuous condition mode operation," *Advances in Electrical and Electronic Engineering*, vol. 14, no. 5, pp. 531-542, 2016.

[17] E. Cengelci, M. Garip, and A. S. Elwakil, "Fractional-order controllers for switching DC/DC converters using the K-factor method: Analysis and circuit realization," *International Journal of Circuit Theory and Applications*, vol. 50, no. 2, pp. 588-613, 2022.

[18] L. Ibarra, I. Macias, P. Ponce, and A. Molina, "On DC/DC voltage buck converter control improvement through the QFT approach," *Proceedings of International Confrence on New Developments in Circuits, Systems, Signal Processing, Communications and Computers*, pp. 183-190, 2015.

[19] A. Sedehi, and M. Mirjafari, "Robust Optimal Controller for Buck Converter Under Parametric Uncertainty: An LQR Approach,"*13th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC)*, 2020, pp. 101-106.

[20] T. K. Nizami, A. Chakravarty, and C. Mahanta, "Analysis and experimental investigation into a finite time current observer based adaptive backstepping control of buck converters," *Journal of the Franklin Institute*, vol. 355, no. 12, pp. 4996-5017, 2018.

[21] S. M. Rozali, N. S. Farhana, M. N. Kamarudin, A. F. Z. Abidin, M. F. a. Rahmat, A. R. Husain, and C. C. Soon, "Robust Control Design of Nonlinear System via Backstepping-PSO with Sliding Mode Techniques," *Modeling, Design and Simulation of Systems: 17th Asia Simulation Conference, AsiaSim, Singapore, 2017, pp.* 27-37.

[22] L. Ardhenta, R. Subroto, and R. Hasanah, "Adaptive backstepping control for Buck DC/DC converter and DC motor," *Journal of Physics*, vol. 1595, no. 1, p. 012025, 2020

[23] H. Al-Baidhani, and M. K. Kazimierczuk, "PWMbased proportional-integral sliding-mode current control of DC-DC boost converter," *IEEE Texas Power and Energy Conference (TPEC)*, Texas, 2018, pp. 1-6.

[24] M. Salimi, J. Soltani, A. Zakipour, and N. R. Abjadi, "Hyper-plane sliding mode control of the DC–DC buck/boost converter in continuous and discontinuous conduction modes of operation," *IET Power Electronics*, vol. 8, no. 8, pp. 1473-1482, 2015.

[25] B. Taheri, M. Sedaghat, M. A. Bagherpour, and P. Farhadi, "A new controller for DC-DC converters based on sliding mode control techniques," *Journal of Control*,

Automation and Electrical Systems, vol. 30, no. 1, pp. 63-74, 2019.

[26] B. Wang, G. Ma, D. Xu, L. Zhang, and J. Zhou, "Switching sliding-mode control strategy based on multi-type restrictive condition for voltage control of buck converter in auxiliary energy source," *Applied Energy*, vol. 228, pp. 1373-1384, 2018.

[27] D. Shuai, Y. Xie, and X. Wang, "Optimal control of Buck converter by state feedback linearization," *7th World Congress on Intelligent Control and Automation*, 2008, pp. 2265-2270.

[28] E. Vidal-Idiarte, L. Martinez-Salamero, H. Valderrama-Blavi, F. Guinjoan, and J. Maixe, "Analysis and design of H/sub/spl infin//control of nonminimum phase-switching converters," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 50, no. 10, pp. 1316-1323, 2003.

[29] S. Buso, "/spl mu/-synthesis of a robust voltage controller for a Buck-Boost converter," *27th Annual IEEE Power Electronics Specialists Conference*, 1996, pp. 766-772.

[30] S. Buso, "Design of a robust voltage controller for a buck-boost converter using/spl mu/-synthesis," *IEEE Transactions on Control Systems Technology*, vol. 7, no. 2, pp. 222-229, 1999.

[31] G. Stein, and J. C. Doyle, "Beyond singular values and loop shapes," *Journal of Guidance, Control, and Dynamics*, vol. 14, no. 1, pp. 5-16, 1991.

[32] G. Sandou, and G. Duc, "Using particle swarm optimization for reduced order  $H\infty$  synthesis," *IFAC Proceedings Volumes*, vol. 42, no. 2, pp. 46-51, 2009.

[33] A. Alfi, A. Bakhshi, M. Yousefi, and H. A. Talebi, "Design and implementation of robust-fixed structure controller for telerobotic systems," *Journal of Intelligent* & *Robotic Systems*, vol. 83, no. 2, pp. 253-269, 2016.

[34] E. S. A. Shahri, A. Alfi, and J. T. Machado, "Fractional fixed-structure  $H\infty$  controller design using augmented lagrangian particle swarm optimization with fractional order velocity," *Applied Soft Computing*, vol. 77, pp. 688-695, 2019.

[35] H. Shokri-Ghaleh, A. Alfi, S. Ebadollahi, A. M. Shahri, and S. Ranjbaran, "Unequal limit cuckoo optimization algorithm applied for optimal design of nonlinear field calibration problem of a triaxial accelerometer," *Measurement*, vol. 164, pp. 107963, 2020.

[36] B. Safaee, S. K. Kamaleddin Mousavi Mashhadi. "Optimization of fuzzy membership functions via PSO and GA with application to quad rotor," *Journal of AI and Data Mining*, vol. 5, no. 1, p.p. 1-10, 2017.

[37] A. G. Sedehi, and A. Alfi, "Swarm-based robust fixed-structure controller design for buck converter using Kharitonov approach: design and experiment," *International Journal of Dynamics and Control*, pp. 1-14, 2022.

[38] zE. Carbajal-Gutierrez, J. Morales-Saldaña, and J. Leyva-Ramos, "Modeling of a single-switch quadratic buck converter," *IEEE transactions on aerospace and electronic systems*, vol. 41, no. 4, pp. 1450-1456, 2005.

[39] R. Erickson, and D. Marsimovic, "Fundamentals of Power Electronics, Kluwer Academic Publishers," *Norwell, MA*, 2001.

[40] J. A. Morales-Saldana, J. Leyva-Ramos, E. E. Carbajal-Gutierrez, and M. G. Ortiz-Lopez, "Average current-mode control scheme for a quadratic buck converter with a single switch," *IEEE transactions on power electronics*, vol. 23, no. 1, pp. 485-490, 2008.

[41] K. Zhou, and J. C. Doyle, *Essentials of robust control*, Prentice hall Upper Saddle River, NJ, 1998.

[42] A. Alireza, "PSO with adaptive mutation and inertia weight and its application in parameter estimation of dynamic systems," *Acta Automatica Sinica*, vol. 37, no. 5, pp. 541-549, 2011.

## کنترل کننده مقاوم مرتبه پایین برای مبدل باک درجه دوم DC-DC: طراحی و ساخت

## على سه دهى'، عليرضا الفى'\* و محمدرضا ميرجعفرى'

۱ دانشکده مهندسی برق، دانشگاه صنعتی شاهرود ، شاهرود، ایران.

<sup>۲</sup>دانشکده علوم، مهندسی و فناوری، دانشگاه ایالتی پنسیلوانیا، ایالات متحده آمریکا.

ارسال ۲۰۲۳/۰۹/۱۰؛ بازنگری ۲۰۲۳/۰۱/۱۲؛ پذیرش ۲۰۲۳/۰۱/۲۴

### چکیدہ:

این مقاله به یک چالش کلیدی در طراحی کنترل کننده مناسب برای مبدلهای DC-DC به منظور تنظیم موثر ولتاژ خروجی در یک بازه زمانی محدود میپردازد. علاوه بر نامینیمم فاز بودن این نوع مبدل، مسئله مهم، یعنی عدم قطعیت پارامتری، این کار را پیچیده تر کند. نظریه کنترل مقاوم یک رویکرد موثر برای مقابله با این مشکل است. با این حال، اجرای آن اغلب به کنترل کنندههایی با مرتبه بالا منجر میشود که ممکن است به دلیل محدودیتهای سختافزاری و محاسباتی عملی نباشد. در این مقاله، یک کنترل کننده مقاوم درجه پایین پیشنهاد میشود که ممکن است به دلیل محدودیتهای کنترل کننده های معمولی مرتبه بالا را برآورده می سازد. بدین منظور، یک مسئله بهینه سازی مقید فرمول بندی میشود و الگوریتمهای تکاملی برای دستیابی به مقادیر بهینه پارامترهای کنترل کننده استفاده میشوند. نتایج شبیه سازی و عملی گزارش می شوند و یک تحلیل مقایسه ای با کنترل کننده بهینه IP برای اثبات کارایی روش پیشنهادی انجام می شود.

**کلمات کلیدی**: مبدل باک درجه دوم، سنتز  $\mu$  کاهش مرتبه، کنترل کننده مقاوم، بهینهسازی.